계속되는 SONY의 유사한 발명과 회로를 검토하게 되었다.

SONY는 좋은 화소회를 많이 발명하여 특허를 보유하고 있으며 검토할 가치는 충분히 있기 때문이다.

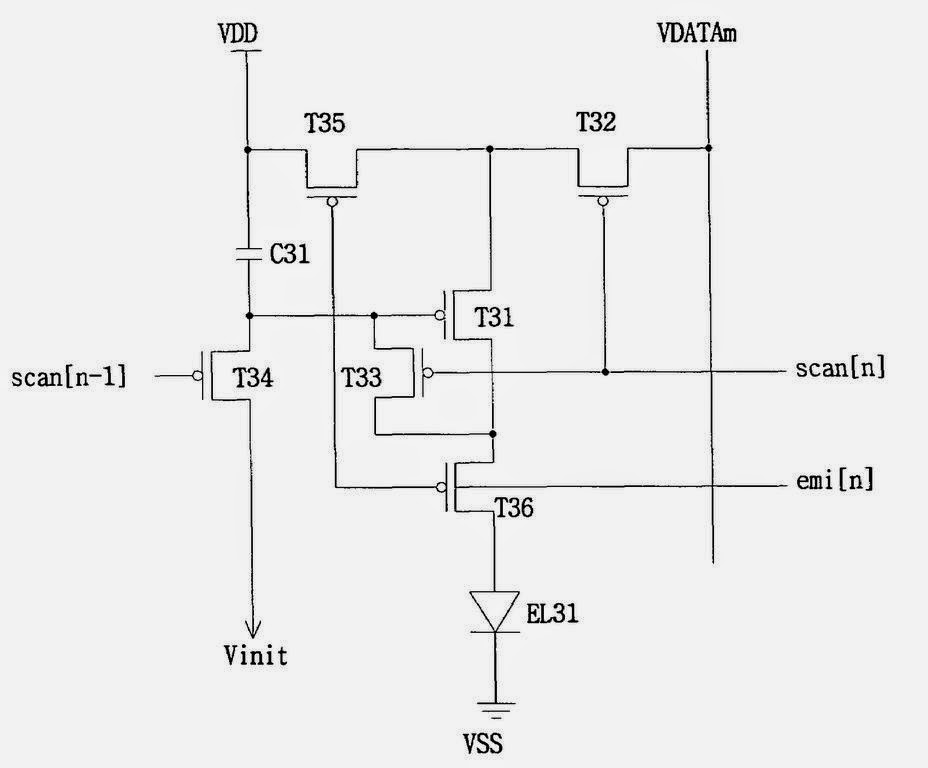

아래는 공개된 3T1C 회로이다.

3T1C회로로써 앞에서 검토한 회로들과 유사점이 많이 있기도 하다.

동작 차트를 보자

타이밍도를 보면서 동작을 보면 아래와 같은 동작을 함을 알수 있다.

(1) 기존 발광

(2) T3 ANODE CLEAR

(3) Vofs 전압 가함

(4) T1 열림

(5) T3 OFF 및 Vth 보상

(6) Vsig 전압 + mobilty 보상

(7) 신규 발광

(1) 기존발광

기존의 데이터를 갖고 발광하는 단계입니다. VG-VS 전압에 따라서 Ids가 결정되고 그 전류에 따라서 EL이 발광하는 상태입니다.

(2) T3 ANODE CLEAR

T3가 켜지면서 S node가 Vss로 낮아지고 동시에 VCC에서 오는 전류도 같이 VSS로 흘러가 버립니다. 이 동작은 마치 A node Clear 와 같으며 또한 VCC OFF와 동일한 효과를 가져옵니다. 다만 VCC와 VSS가 short나는듯이 전류가 많이 흘러 소량의 소비전력의 증가는 어쩔수 없을것으로 보입니다. 다만 TR 1개를 줄이는 효과가 있으니 좋은 아이디어입니다.

(3) Vofs 전압 가함

데이터 배선에 Vofs 전압을 가합니다.

(4) T1 열림

T1이 열리면서 G node에 Vofs를 가합니다.

(5) T3 OFF 및 Vth 보상

S node에 VSS를 가하던 T3를 오프시키면서 동시에 Vth 보상이 시작됩니다.

자주 보셨던 그림이죠?

(6) Vsig 전압 + mobilty 보상

Vth 가 충분한 시간동안 이루어지면 곧바로 실제 원하는 데이터인 Vsig를 가합니다. 이때 항상동일했지만 S node에는 T2의 mobility에 따라서 전압 상승도가 다르게 되고 이때 mobility가 보상되는 동작을 합니다.

(7) 신규 발광

T1이 이제는 꺼지면서 다시 새로운 데이터 값이 써진 Ids를 보내게 됩니다.

이로써 동작들을 정리하였습니다.

그러나 본 특허에서는 후반부에 Vth를 나누어서 하는 방법을 추가로 제시하였습니다.

실제로 SONY의 특허에는 이렇게 Vth보상을 여러시간동안 나누어서하는 특허가 많습니다. 아무래도 1H라는 시간이 해상도에 따라서 짧아지고 그 짧아진 시간동안 S node전압이 충분히 Vofs-Vth 전압까지 오지 못하는 경우가 발생할수 있습니다. 그러므로 그러한 한계를 극복하기 위해서 여러번 나누어서 Vth를 보상하는 방법을 사용합니다.

위의 타이밍 차트에서 보듯이 T1이 켜지면서 G node에 Vofs를 가하면서 Vth 보상을 하다가 잠깐 T1을 끄고 데이터 배선이 Vsig가 됩니다. 그러나 이때는 T1을 끄죠 그 Vsig은 아마 전 라인의 데이터인것 같습니다. 그 전 데이터를 쓰고 다시 T1을 켜고 Vofs를 가하여 충분한 Vth를 보상한후 Vsig를 넣어서 보상을 마치고 종료를 하는 것을 볼수 있습니다.

데이터 배선에 데이터와 Vofs를 계속 전환 해야 하기 때문에,

고해상도로 갈수록 data charging에 불리 하지 않을까 걱정됩니다.

더 자세한 특허 명세서는 아래의 LINK를 보시면 됩니다.

GOOGLE PATENT LINK